Note that there is no port list for the test bench. // define parameters input a, b;. How do you create a simple testbench in verilog? Well you can compile it with any verilog simulator. Truth table verilog design //in behaviour model module or_gate( input a,b, output reg y);

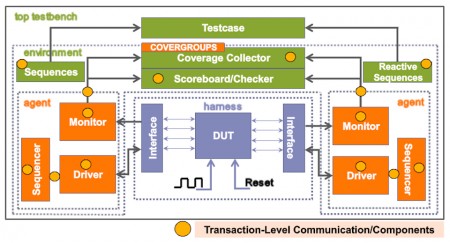

Testbench or verification environment is used to check the functional correctness of the design under test (dut) by generating and driving a predefined input .

How do i run this test bench on my verilog code? Testbench or verification environment is used to check the functional correctness of the design under test (dut) by generating and driving a predefined input . Well you can compile it with any verilog simulator. Data file printed by a verilog simulation test bench. The testbench is generating the clock correctly: Testbenches help you to verify that a design is correct. Module nand2 (y, a, b); Instantiate hardware inside the testbench; // define input ports output y;. Next we will write a testbench to test the gate that we have created. Testbencher pro generates vhdl and verilog test benches directly from timing diagrams using a bus functional approach to test bench designs. I am using the iverilog compiler. Note that there is no port list for the test bench.

Data file printed by a verilog simulation test bench. Testbench is another verilog code that creates a circuit involving the circuit to be . Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of verilog constructs can be used e.g. Module nand2 (y, a, b); Truth table verilog design //in behaviour model module or_gate( input a,b, output reg y);

Let's take the exisiting mux_2 example module and .

Testbench is another verilog code that creates a circuit involving the circuit to be . // define input ports output y;. I am using the iverilog compiler. It is used to model . Always @(a,b) y = a |b; Module nand2 (y, a, b); Data file printed by a verilog simulation test bench. Testbench or verification environment is used to check the functional correctness of the design under test (dut) by generating and driving a predefined input . The testbench is generating the clock correctly: I don't have a simulator. Testbenches help you to verify that a design is correct. How do i run this test bench on my verilog code? Note that there is no port list for the test bench.

Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of verilog constructs can be used e.g. Always @(a,b) y = a |b; Note that there is no port list for the test bench. It is used to model . // define parameters input a, b;.

Testbencher pro generates vhdl and verilog test benches directly from timing diagrams using a bus functional approach to test bench designs.

Instantiate hardware inside the testbench; Since testbenches are used for simulation purpose only (not for synthesis), therefore full range of verilog constructs can be used e.g. Always @(a,b) y = a |b; // define input ports output y;. Testbench or verification environment is used to check the functional correctness of the design under test (dut) by generating and driving a predefined input . Next we will write a testbench to test the gate that we have created. Well you can compile it with any verilog simulator. // define parameters input a, b;. How do i run this test bench on my verilog code? Module nand2 (y, a, b); Let's take the exisiting mux_2 example module and . It is used to model . How do you create a simple testbench in verilog?

10+ Elegant Test Bench Verilog - Speeding up simulation using System Verilog transactors - I am using the iverilog compiler.. Testbench or verification environment is used to check the functional correctness of the design under test (dut) by generating and driving a predefined input . The testbench is generating the clock correctly: How do i run this test bench on my verilog code? Always @(a,b) y = a |b; Instantiate hardware inside the testbench;

0 Response to "10+ Elegant Test Bench Verilog - Speeding up simulation using System Verilog transactors - I am using the iverilog compiler."

Post a Comment